20nm FPGAæ┬įęÄäØ │¼įĮ║åå╬╣ż╦ć╔²╝ē

üĒį┤Ż║ļŖūėł¾

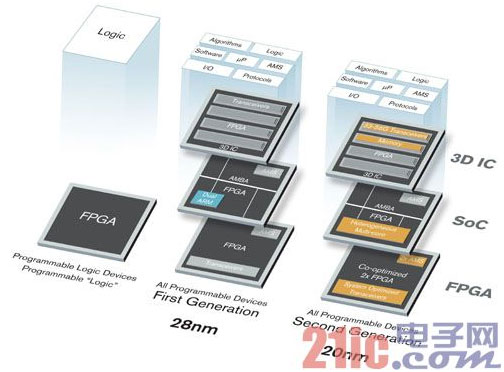

ĪĪĪĪ─┐Ū░Ż¼┼_ĘeļŖ28nm┴╝┬╩┤¾Ę∙╠ß╔²Ą─└¹║├▀Ćø]▒╗╩ął÷ÅžĄūŽ¹╗»Ż¼FPGAśIĮńļpą█ęčĀÄŽ╚┐ų║¾Ąž░l▓╝20nm FPGAæ┬įęÄäØŻ¼į┌ąį─▄Īó╣”║─Īó╝»│╔Č╚Ą╚ĘĮ├µŠ∙┤¾Ę∙▄S╔²Ż¼ąQ╩│ASICų«ä▌īóė·č▌ė·┴ęĪŻį┌45nm╣ż╦ć╣سcŻ¼┤¾┴┐ASICÅS╔╠┬╩Ž╚┴┐«a;Č°ĄĮ┴╦28nm╣ż╦ćĢr┤·Ż¼┬╩Ž╚┴┐«aĄ─7╝ę╣½╦Šųąęčėąā╔╝ę╩ŪFPGAÅS╔╠;į┌20nmĢr┤·Ż¼FPGA╗“īó░╬Ą├Ņ^╗IĪŻ

ĪĪĪĪ│¼įĮ║åå╬╣ż╦ć╔²╝ē

ĪĪĪĪFPGAŽ“Ž┬ę╗┤·╣ż╦ćč▌▀M▓ó▓╗╩Ū"╔²╝ē"─Ū├┤║åå╬Ż¼ąĶę¬ųTČÓäōą┬╝╝ągæ¬ī”╠¶æĪŻ

ĪĪĪĪ▀~Ž“Ė³Ė▀╣ż╦ć╩Ū╩ął÷“īäė┴”╦∙ų┬ĪŻ"─┐Ū░¤oŠĆ═©ą┼ĪóęĢŅlŽ¹┘MĪóŲ¹▄ćĖ▀╝ē▌oų·±{±éĪóßt»¤ļŖūėĪó░▓Ę└╝╝ągĄ╚æ¬ė├ĮoFPGA╠ß│÷┴╦Š▐┤¾Ą─ąĶŪ¾Ż¼ę¬ØMūŃ╚ń┤╦┐ņ╦┘į÷ķLĄ─╠Ä└ĒąĶŪ¾Ż¼▒žĒÜīŹ¼FĖ▀╝»│╔Ż¼Č°ę¬īŹ¼FĖ▀╝»│╔▒žĒÜŽ“Ė▀╝ē╣ż╦ć▀węŲŻ¼▓óęįäōą┬Ą─╦╝┬ĘüĒĮŌøQ╝»│╔╠¶æĪŻ"┘Éņ`╦╝╣½╦Š╚½Ū“Ė▀╝ēĖ▒┐é▓├Īóüå╠½ģ^ł╠ąą┐é▓├£½┴ó╚╦ÅŖš{ĪŻę“┤╦Ż¼ļm╚╗28nm FPGA«aŲĘį┌Į±─Ļ▓┼┴┐«a│÷žøŻ¼Ą½FPGAÅS╔╠ģsęčŽ╚ąąę╗▓ĮŽ“20nm░l┴”Ż¼ęįØMūŃ╩ął÷ī”┐╔ŠÄ│╠▀ē▌ŗ│╩ųĖöĄ╝ēį÷ķLĄ─ąĶŪ¾ĪŻ

ĪĪĪĪŽ“Ž┬ę╗┤·╣ż╦ćč▌▀M▓ó▓╗╩Ū"╔²╝ē"─Ū├┤║åå╬Ż¼ąĶę¬ųTČÓäōą┬╝╝ągæ¬ī”╠¶æĪŻį┌28nm╣ż╦ć╣سc╔ŽŻ¼┘Éņ`╦╝┬╩Ž╚═Ų│÷┴╦ĮyAll ProgrammableĄ─7ŽĄ┴ąFPGAĪóŪČ╚ļARM cortex-A9Ą─FPGA SoCęį╝░▓╔ė├3DĘŌčb╝╝ągĄ─Virtex-7 2000TŻ¼┘Éņ`╦╝20nm«aŲĘę└╚╗╩Ū╚²éĆ«aŲĘŽĄ┴ą▓óąą░lš╣Ż¼Ęųäe"▀M╗»"│╔8ŽĄ┴ąFPGAĪóĄ┌Č■┤·FPGA SoC║═Ą┌Č■┤·3DĘŌčbFPGAĪŻ┘Éņ`╦╝20nm 8ŽĄ┴ąAll Programmable FPGAīóėąĖ³┐ņĄ─DSPĪóBRAM(Block RAM)ĪóDDR4╝░╩š░lŲ„Ż¼ėąĖ▀Ą─ĦīÆ(100éĆ33Gb/s╩š░lŲ„)Ż¼┐╔ęįīŹ¼FĖ³Ė▀Ą─ĦīÆ┐éŠĆ║═Ė³┐ņĄ─įOėŗ╩šö┐ĪŻ┼c7ŽĄ┴ą«aŲĘŽÓ▒╚Ż¼Ųõąį─▄╠ßĖ▀┴╦2▒ČŻ¼╣”║─ĮĄĄ═┴╦ę╗░ļŻ¼╝»│╔Č╚ät╠ßĖ▀┴╦1.5Ī½2▒ČĪŻį┌FPGA SoCĘĮ├µŻ¼┘Éņ`╦╝ŪČ╚ļ┴╦ARM Cortex-A9ļp║╦╠Ä└ĒŲ„Ą─28nm ZYNQŽĄ┴ą«aŲĘęčĮø┴┐«a│÷žøŻ¼"┘Éņ`╦╝20nm FPGA SoCīó▓╗Ą½ŪČ╚ļARM╠Ä└ĒŲ„Ż¼ę▓īóŪČ╚ļŲõ╦¹╠Ä└Ēå╬į¬Ż¼└²╚ńDSPĪóņ`╗Ņ╗ņ║Žą┼╠¢(AMS)ęį╝░Įø“×ūCĄ─Video IPĪó╦ŃĘ©Ą╚Ą╚Ż¼╦³▀Ćīó▓╔ė├AXI┐éŠĆĪŻ"£½┴ó╚╦ĮķĮBšfŻ¼"Į±║¾▀Ćėą┐╔─▄ŪČ╚ļąį─▄Ė³Ė▀ĪóĖ³ČÓĄ─ARM║╦ĪŻ"

ĪĪĪĪFPGA┴Ēę╗ųžę¬╣®æ¬╔╠Alteraį┌20nm╣ż╦ćę▓ī¦╚ļ┴╦╚²ĒŚą┬╝╝ągĪŻAlteraĖ▀╝ēĖ▒┐é▓├Īó╩ūŽ»╝╝ąg╣┘Misha BurichĮķĮBŻ¼AlteraĄ─20nm╣ż╦ćFPGAę╗╩Ū┐╔īóąŠŲ¼ķgĄ─öĄō■é„▌ö╦┘Č╚╠ßĖ▀ų┴40GbpsŻ¼Č°¼FąąĄ─28nm╣ż╦ćFPGA×ķ28GbpsĪŻ×ķ┴╦īŹ¼FĖ▀╦┘╗»Ż¼20nm╣ż╦ćFPGA╠ßĖ▀┴╦╩š░lŲ„ļŖ┬Ę╩╣ė├Ą─Š¦¾w╣▄ąį─▄Ż¼═¼Ģrī¦╚ļ┴╦Ė∙ō■į┌ąŠŲ¼ķgĮ╗ōQą┼╠¢Ą─▓©ą╬üĒą▐š²ą┼╠¢ĪóĖ─╔Ųą┼╠¢Ė╔ö_╝░╦ź£p│╠Č╚Ą─ļŖ┬Ę╝╝ągĪŻČ■╩Ū┼õéõĖĪ³c▀\╦Ńąį─▄▀_ĄĮ5TFLOPS(├┐├ļ5╚fā|┤╬ĖĪ³c▀\╦Ń)ęįŽ┬Ą─┐╔ūāŠ½Č╚DSP─ŻēKĪŻ×ķ┴╦╠ßĖ▀ąį─▄Ż¼īóįŁüĒė├▄ø╝■īŹ¼FĄ─DSP▓┐Ęų▀\╦Ń╠Ä└ĒĖ─×ķ┴╦ė▓╝■▓┘ū„ĪŻ╚²╩Ū«Éśŗ3D ICĄ─æ¬ė├ĪŻ

ĪĪĪĪ3D IC╝╝ąg╝ė┐ņ░lš╣

ĪĪĪĪū„×ķą┬╝╝ągŻ¼3D ICąĶę¬Ė³║├ĪóĖ³│╔╩ņĄ─įOėŗ║═£yįć╣żŠ▀▓┼─▄▒╗śIĮńÅVĘ║Įė╩▄ĪŻ

ĪĪĪĪį┌ųTČÓäōą┬ųąŻ¼╬³ę²č█Ū“Ą─╩Ū3D IC╝╝ągį┌═¼śŗų«═ŌŻ¼«Éśŗ╝╝ągę▓īó╝ė┐ņ░lš╣ĪŻ"«Éśŗ3D IC╝╝ąg┐╔īóFPGA┼cęįŪ░═Ōų├Ą─ąŠŲ¼╝»│╔į┌═¼ę╗ĘŌčbųąŻ¼▓╗āH┐╔╩╣ąŠŲ¼ķgĄ─▓╝ŠĆŠÓļx┐sČ╠Ż¼Č°Ūę▀Ć┐╔┤¾┤¾į÷╝ėąŠŲ¼ķgĄ─▓╝ŠĆĖ∙öĄŻ¼┤¾Ę∙╠ßĖ▀ąŠŲ¼ķgĄ─öĄō■é„▌ö╦┘Č╚(ŽĄĮyąį─▄)Ż¼Č°ę“×ķąŠŲ¼ķg▓╝ŠĆŠÓļx┐sČ╠╝░Įė┐┌▓╝ŠĆļŖ╚▌£p╔┘Ą╚įŁę“Ż¼─▄ē“ĮĄĄ═ŽĄĮy╣”║─ĪŻ"Misha BurichųĖ│÷ĪŻ

ĪĪĪĪ┘Éņ`╦╝Ą─3D IC«aŲĘęÄäØęčÅ─│§Ą─═¼śŗŽĄĮy░lš╣ĄĮ«ÉśŗŽĄĮyŻ¼╚ńį┌28nm╣سcŻ¼┘Éņ`╦╝┬╩Ž╚═Ų│÷Ą─virtex-7 200T╩Ū═¼śŗŲ„╝■Ż¼║¾üĒ═Ų│÷Ą─Virtex-7 H580Tät╩Ū«ÉśŗŲ„╝■Ż¼į┌28nm╣ż╦ćĄ─FPGA╔ŽĘŌčb┴╦45nm╣ż╦ćĄ─28Gbps╩š░lŲ„Ż¼¼Fį┌┘Éņ`╦╝20nm 3D ICę▓īó╠ß╣®═¼śŗ║═«Éśŗā╔ĘN┼õų├ĪŻ£½┴ó╚╦ųĖ│÷Ż¼20nm 3D IC▓╗Ą½ėą56Gbps╩š░lŲ„Ż¼▀ĆĘŌčbėąĖ³┤¾╚▌┴┐Ą─┤µā”Ų„Ż¼ļm╚╗ĘŌčbļyČ╚╝ė┤¾Ż¼Ą½┘Éņ`╦╝ęčĮøĮŌøQ┴╦║▄ČÓļyŅ}Ż¼▀@īó╩Ūę╗ĘN╚½ą┬Ą─3D ICŲ„╝■ĪŻ

ĪĪĪĪAlteraĄ─«Éśŗ3D IC╝╝ągät═©▀^äōą┬Ą─Ė▀╦┘╗ź┬ōĮė┐┌üĒ╝»│╔FPGA║═ė├æ¶┐╔Č©ųŲHardCopy ASICŻ¼╗“š▀╝»│╔░³└©┤µā”Ų„ĪóĄ┌╚²ĘĮASICĪó╣ŌĮė┐┌Ą╚į┌ā╚Ą─Ė„ĘN╝╝ągĪŻ═¼ĢrŻ¼20nm╗ņ║ŽŽĄĮy╝▄śŗį┌╣”║─╣▄└ĒĘĮ├µ└^└mäōą┬Ż¼░³└©ūį▀mæ¬ļŖē║š{š¹Īó┐╔ŠÄ│╠╣”║─╝╝ągęį╝░╣ż╦ć╝╝ągā×╗»Ą╚Ż¼╩╣Ą├AlteraŲ„╝■╣”║─▒╚Ū░ę╗┤·ĮĄĄ═┴╦60%ĪŻ

ĪĪĪĪ«ö╚╗Ż¼3D IC╝╝ąg┐┤╔Ž╚ź║▄├└Ż¼Ą½šµš²┤¾ęÄ─Ż╩╣ė├▀Ćę¬ĮŌøQųTČÓ╠¶æĪŻMentor Graphics╣½╦ŠČŁ╩┬Ģ■ų„Ž»╝µCEO Wally Rhinesį°▒Ē╩ŠŻ¼2.5D(SiP)╝╝ąg─┐Ū░╚į╚╗ø]ėą░lō]ĄĮśOų┬Ż¼2.5D ICĄ─┤µį┌Ģrķgīó▒╚śIĮńŲš▒ķŅAŲ┌Ą─ę¬Ė³ķLę╗ą®ĪŻū„×ķą┬╝╝ągŻ¼3D ICąĶę¬Ė³║├ĪóĖ³│╔╩ņĄ─įOėŗ║═£yįć╣żŠ▀▓┼─▄▒╗śIĮńÅVĘ║Įė╩▄ĪŻ

ĪĪĪĪįOėŗ╣żŠ▀┼cĢrŠŃ▀M

ĪĪĪĪįOėŗ╣żŠ▀ßśī”20nm«aŲĘŽĄ┴ą▀Mąą┴╦▀Mę╗▓Įģf═¼ā×╗»Ż¼īóįOėŗą¦┬╩╠ßĖ▀ĄĮą┬Ą─īė╝ēĪŻ

ĪĪĪĪš²╦∙ų^"║├±R┼õ║├░░"Ż¼ę¬ūī║├Ų„╝■░lō]│÷┤¾ą¦─▄ę▓ąĶę¬ėąĖ³║├Ą─įOėŗ╣żŠ▀üĒų¦│ųĪŻ

ĪĪĪĪ┼c┘Éņ`╦╝7ŽĄ┴ą28nm«aŲĘŽĄ┴ąę╗═¼═Ų│÷Ą─VivadoįOėŗ╠ū╝■Ż¼ßśī”20nm«aŲĘŽĄ┴ą▀Mąą┴╦▀Mę╗▓Įģf═¼ā×╗»Ż¼īóįOėŗą¦┬╩╠ßĖ▀ĄĮą┬Ą─īė╝ēĪŻ£½┴ó╚╦ĮķĮBšfŻ¼ą┬Ą─VivadoįOėŗ╠ū╝■┐╔ūīįOėŗ╚╦åTīóLUT└¹ė├┬╩╠ß╔²20%Ż¼ąį─▄╠ß╔²3éĆ╦┘Č╚Ą╚╝ēŻ¼╣”║─ĮĄĄ═35%Ż¼įOėŗ╔·«a┴”╠ß╔²4▒ČĪŻ┤╦═ŌŻ¼į┌┼õ║ŽCšZčįįOėŗ┴„│╠╩╣ė├ĢrŻ¼“×ūC▀\ąąĢrķg┐sČ╠100▒ČĪŻRTLĘ┬šµ║═ė▓╝■ģf═¼Ę┬šµ╦┘Č╚┐ņ3Ī½100▒ČĪŻČ°Ūę└¹ė├VivadoĄ─IP╝»│╔Ų„║═ĘŌčbŲ„īŹ¼FIPųžė├┐╔īó╝»│╔╦┘Č╚╝ė┐ņ4Ī½5▒ČĪŻ

ĪĪĪĪ"ą┬Ą─VivadoįOėŗ╠ū╝■┐╔īóęįŪ░Ą─ÄūéĆį┬įOėŗų▄Ų┌┐sČ╠ĄĮÄūų▄Ż¼▀@╩ŪįOėŗą¦┬╩Ą─┤¾Ę∙Č╚╠ß╔²ĪŻ"£½┴ó╚╦ÅŖš{Ż¼"═©▀^┼c┘Éņ`╦╝VivadoįOėŗ╠ū╝■ßśī”Ė▀╔·«a┴”║═ĮY╣¹┘|┴┐Ą─ģf═¼ā×╗»Ż¼20nm«aŲĘŽĄ┴ąīó─▄ē“×ķąąśI╠ß╣®Ė³Š▀╬³ę²┴”Ą─ASIC║═ASSP┐╔ŠÄ│╠╠µ┤·ĘĮ░ĖĪŻ"

ĪĪĪĪČ°AlteraĄ─«Éśŗ20nm FPGAĄ─ķ_░l═©▀^╚½╣”─▄Ė▀╝ēįOėŗŁhŠ│Ą├ęįīŹ¼FŻ¼▀@ę╗įOėŗŁhŠ│░³└©ŽĄĮy╝»│╔╣żŠ▀(Qsys)Īó╗∙ė┌CšZčįĄ─įOėŗ╣żŠ▀(OpenCL)ęį╝░DSPķ_░l▄ø╝■(DSP Builder)ĪŻMisha Burich▒Ē╩ŠŻ¼Ž┬ę╗┤·Ė▀ąį─▄įOėŗDSPķ_░l╚╦åT▓╗į┘ąĶę¬╗©┘MöĄ╠ņ╔§ų┴ÄūéĆąŪŲ┌Ą─ĢrķgüĒįu╣└FPGA DSPĮŌøQĘĮ░ĖĄ─ąį─▄ĪŻ═©▀^╝»│╔OpenCL║═DSPäōą┬╝╝ągŻ¼▓╔ė├śIĮńś╦£╩įOėŗ╣żŠ▀║═▄ø╝■ÄņŻ¼Altera«aŲĘ─▄ē“īŹ¼F5 TFLOPSĄ─å╬Š½Č╚DSP─▄┴”Ż¼▀@īóųžą┬śõ┴óśIĮńTFLOPS/W╣ĶŲ¼ą¦┬╩Ą─ś╦£╩ĪŻ

¤ß³cµ£ĮėŻ║

1Īó╬ó▄øŪČ╚ļ╩ĮWindows Embedded 8ķ_äōųŪ─▄ŽĄĮyą┬Ģr┤·

2Īó╣╚ĖĶ╝┤īó╚½├µ═Ų╦═Android 4.2.1Ė³ą┬

3ĪóŠGČŠŪ░└Ž┤¾Ż║iOS6įĮ¬zŪ░Š░▓╗├„└╩

4ĪóFacebook╣─äŅåT╣ż╩╣ė├Android╩ųÖC

5ĪóJava“īäėį┌ųŪ─▄ŪČ╚ļ╩ĮįOéõ╔ŽĖ³Š▀ā×ä▌